## COM2 Enhanced Graded Base SiGe Technology for High Speed Applications

T. Ivanov, Michael Carroll, S. Moinian\*, M. Mastrapasqua\*, M. Frei\*, A. Chen, C. King\*, A. Hamad, E. Martin, S. Shive, T. Esry, C. Lee, R. Johnson\*, T. Sorsch\*, Malcolm Carroll\*, K. Banoo\*, P. Smith and W. Cochran

Agere Systems, 9333 S. John Young Pkwy., Orlando, FL 32819

\* Agere Systems, Murray Hill, NJ

**Abstract** The COM2 Enhanced Graded Base SiGe modular BiCMOS technology has been developed. It is based on the COM2 digital CMOS process. The technology achieves peak  $F_t=100$  GHz, peak  $F_{max}=101$  GHz, peak  $\beta=186$  and  $BV_{ceox}=2.05$  V.  $F_t \cdot BV_{ceox}$  product of 205 and good across wafer uniformity are demonstrated.

### I. INTRODUCTION

The requirements of high speed data networks have proven to be one of the main drivers for development of advanced BiCMOS processes. Currently, 40 Gb/s data rates are being approached with a number of different system architectures, chip solutions and technology mixes. The SiGe BiCMOS technology presented targets high-speed section of 40 GHz data transceivers.

### II. COM2 CMOS PLATFORM

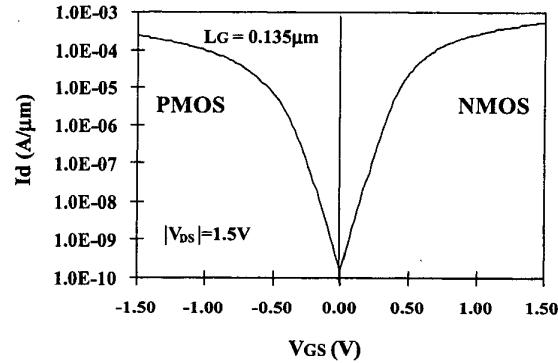

The SiGe technology is modular and is based on Agere Systems' COM2 digital process [1]. Summary of COM2 CMOS transistor parameters is given in Table 1. Three different types of CMOS devices comprise the digital core: 1) High Performance ( $V_{DD}=1.5$  V,  $L_G=0.135$   $\mu$ m); 2) Low Power ( $V_{DD}=1.5$  V,  $L_G=0.145$   $\mu$ m); 3) High Voltage ( $V_{DD}=3.3$  V,  $L_G=0.32/0.28$   $\mu$ m). Figure 1 shows a plot of  $I_D$  vs.  $V_{GS}$  for the high performance device. The core process has shallow trench isolation and 6 levels of metal. Enhancement modules can be added to the core in order to meet application specific requirements. It is possible to integrate such modules as SRAM [3], MOM capacitor, linear GOX capacitor, high Q inductor [4], precision resistor, fuse/trim link, low  $V_{TH}$  device and a variety of resistors without changing the parameters of the core CMOS devices. SiGe bipolar devices are also built with a modular approach [2] and can be added to the mix for high speed performance.

Fig. 1 NMOS and PMOS  $I_D$  vs.  $V_{GS}$

### III. SiGe NPN TRANSISTOR

The current device is an enhanced version of the previously reported SiGe graded base process [1]. Improvements were made in the emitter-base junction formation and collector engineering. The SiGe NPN transistor is built using 6 masks (Deep Trench, High Energy Implanted Collector, Collector Sinker, Emitter Window, Emitter Poly and Base Poly).

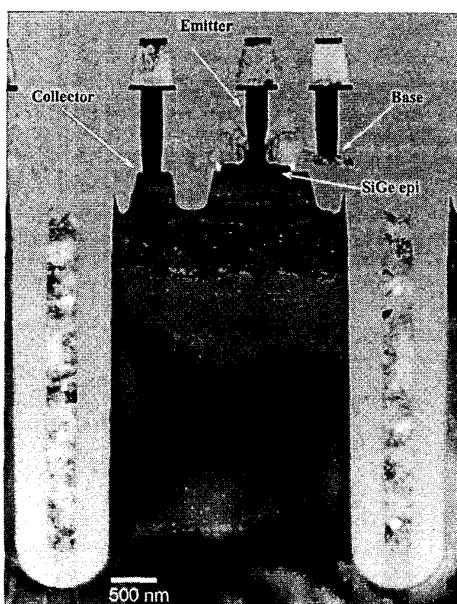

Figure 2 shows micrograph of the transistor from recent material. The deep trench has composite oxide / polysilicon fill. It is 1  $\mu$ m wide and approximately 4.5  $\mu$ m deep. The measured data is the one that was originally submitted for this conference. It is from material with the same vertical profile, LOCOS isolation (instead of STI) and without deep trench.

One additional mask can be used to produce dual voltage (1.8 and 2.5 V) device libraries. A  $BV_{ceox}$  of 2V is sufficient for building circuits for the applications of interest and therefore gives us the best trade-off for speed.

Table I

COM2 CMOS Parameters

|                                                          | High Performance | Low Power      | High Voltage |

|----------------------------------------------------------|------------------|----------------|--------------|

| $V_{DD}$ (V)                                             | 1.5              | 1.5            | 3.3          |

| $T_{OX}$ (nm)                                            | 2.4              | 2.4            | 5.0          |

| $L_G$ ( $\mu\text{m}$ ) NMOS/PMOS                        | 0.135/0.135      | 0.145/0.145    | 0.32/0.28    |

| Nominal $I_{ON}$ ( $\mu\text{A}/\mu\text{m}$ ) NMOS/PMOS | 575/255          | 390/170        | 700/400      |

| Worst-case $I_{OFF}$ ( $/\mu\text{m}$ ) NMOS/PMOS        | 3nA/3nA          | 10pA/10pA      | 100pA/100pA  |

| $V_{t\text{-lin}}$ (V) NMOS/PMOS                         | 0.41/0.41        | 0.55/0.55      | 0.55/0.90    |

| Ring oscillator delay (ps/stage)                         | 24               | 34             | 30           |

| Drain engineering                                        | halo/extension   | Halo/extension | LD           |

Fig. 2 Micrograph of COM2 SiGe NPN device with deep trench isolation

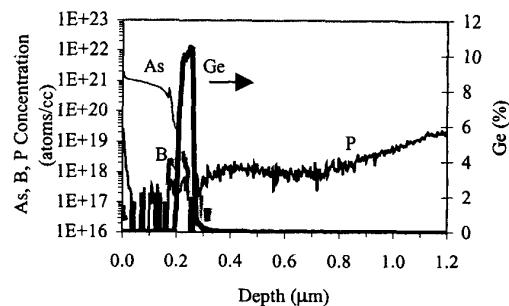

A precision base poly resistor is provided using optional mask. The npn device has a reduced link-base resistance because it is super-self-aligned. SiGe boron doped base is grown using selective epitaxy, and a built-in electric field is engineered in the base by grading the Ge profile from approximately 12% to zero. The emitter-base junction is formed through out-diffusion from *in-situ* arsenic doped poly. The measured doping profile of the emitter window region is provided in Fig. 3.

Fig. 3 SIMS profiles for SiGe NPN device

#### IV. EXPERIMENTAL RESULTS

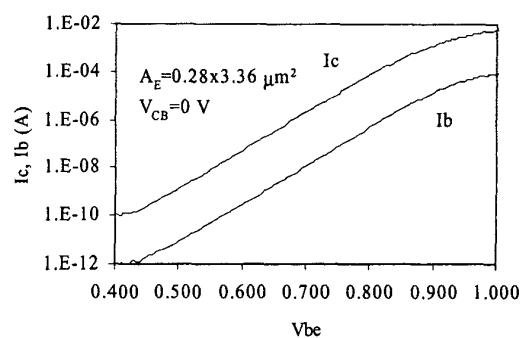

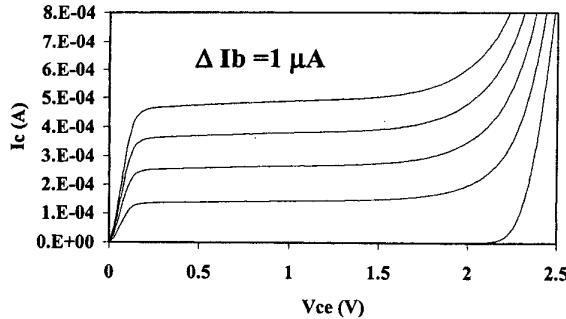

A typical Gummel plot shown on Fig. 4 exhibits near ideal base and collector currents down to low  $V_{BE}$  bias. The collector characteristics shown in Fig. 5 with  $\Delta I_B = 1 \mu\text{A}$  exhibit a breakdown voltage of  $\sim 2.1\text{V}$ .

Fig. 4. Gummel plot for  $0.28 \times 3.36 \mu\text{m}^2$  SiGe NPN

Fig. 5. Collector characteristics of  $0.28 \times 3.36 \mu\text{m}^2$  NPN

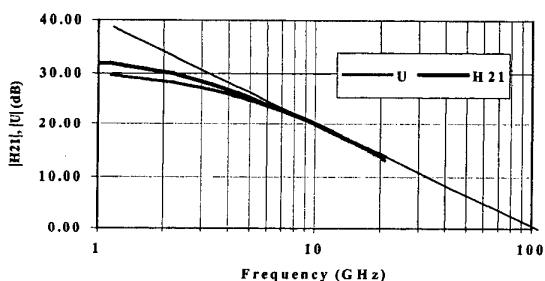

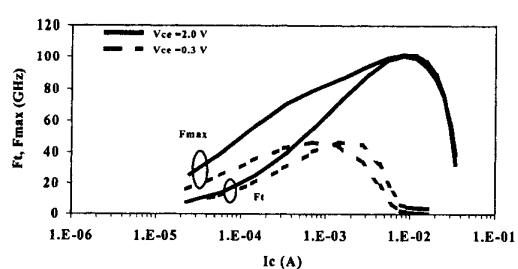

The high frequency performance of the SiGe NPN device is presented in Fig. 6 and Fig. 7. The first figure shows the magnitudes of the small signal short circuit current gain and Mason's unilateral power gain as a function of frequency with the device biased for peak  $F_T$  operation. The device was engineered for an optimum exchange of  $F_T$  for  $F_{MAX}$  and thus the two gain curves almost overlap. Extrapolated -20 dB/decade lines measure  $F_T=100$  GHz and  $F_{MAX}=101$  GHz. Fig. 7 provides more details about the  $F_T$  and  $F_{MAX}$  behavior as a function of  $I_C$  and  $V_{CE}$ .

Fig. 6  $|h_{21}|$  and  $|U|$  vs. freq. for  $6 \times 0.28 \times 1.12 \mu\text{m}^2$  SiGe NPN

Fig. 7  $F_T$  and  $F_{MAX}$  vs  $I_C$  and  $V_{CE}$  for  $6 \times 0.28 \times 1.12 \mu\text{m}^2$  SiGe NPN

$F_T \cdot BV_{CE}$  product of 205 is achieved. For  $V_{CE}=0.3\text{V}$ ,  $F_T$  and  $F_{MAX}$  have peak values of 47 GHz and 46 GHz demonstrating that high performance can still be achieved in applications requiring low headroom. SiGe NPN transistor measured data is presented in Table 2 for device with  $A_E = 0.28 \times 3.36 \mu\text{m}^2$ .

Table II

COM2 SiGe NPN Measured Parameters

|                                                              |                                  |

|--------------------------------------------------------------|----------------------------------|

| Emitter size                                                 | $0.28 \times 3.36 \mu\text{m}^2$ |

| Beta                                                         | 186                              |

| $V_A$ (V)                                                    | 74                               |

| $BV_{CE}$ (V)                                                | 2.05                             |

| $F_T$ (GHz) at $I_C=4.0\text{mA}$ , $V_{CE}=2\text{V}$       | 103                              |

| $F_T$ (GHz) at $I_C=1.0\text{mA}$ , $V_{CE}=0.3\text{V}$     | 47                               |

| $F_{MAX}$ (GHz) at $I_C=0.6\text{mA}$ , $V_{CE}=2\text{V}$   | 105                              |

| $F_{MAX}$ (GHz) at $I_C=0.3\text{mA}$ , $V_{CE}=0.3\text{V}$ | 47                               |

| $C_{BE}$ (fF)                                                | 8.5                              |

| $C_{BC}$ (fF)                                                | 7.3                              |

| $C_{CS}$ (fF)                                                | 20.7                             |

| $F_T \cdot BV_{CE}$ Product (GHz*V)                          | 211.2                            |

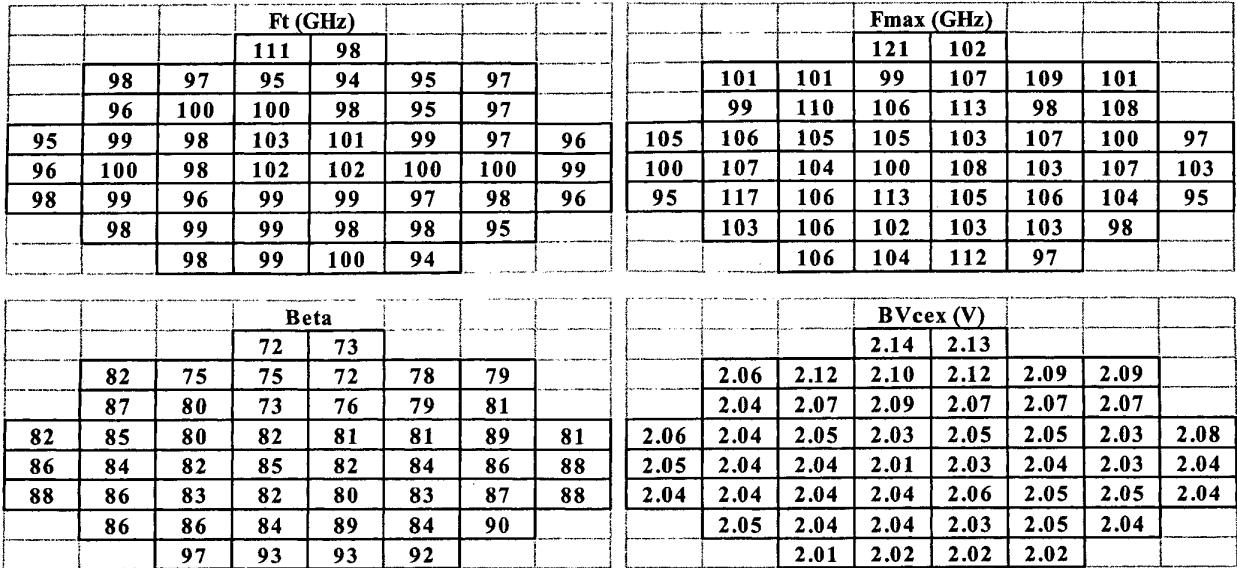

Fig. 8 shows wafer maps of key device parameters including  $F_T$ ,  $F_{MAX}$ , current gain, and collector-emitter breakdown voltage. The devices are biased for peak  $F_T$  operation.  $F_T$  across wafer is in the range 94 - 111 GHz with majority of the data points clustered at  $\sim 100$  GHz.  $F_{MAX}$  varies from 95 GHz to 121 GHz with average value of 104 GHz. The DC current gain has an average value of 83. The  $BV_{CE}$ , measured at  $I_C=1\mu\text{A}$  when  $I_B=1\text{nA}$ , is in the range 2.01 to 2.14 V. The parameter statistics are summarized in Table 3.

Table III

Statistics of NPN Parameters Calculated from Wafer Maps

(measured at  $I_C=4.0\text{mA}$ ,  $V_{CE}=2\text{V}$ )

| Parameter | Mean  | St. Deviation |

|-----------|-------|---------------|

| $F_T$     | 98.2  | 2.7           |

| $F_{MAX}$ | 104.4 | 5.3           |

| $\beta$   | 83.2  | 5.6           |

| $BV_{CE}$ | 2.05  | 0.03          |

Fig. 8. Ft, Fmax,  $\beta$  and BVcex wafer maps for  $0.28 \times 3.36 \mu\text{m}^2$  COM2 SiGe NPN (measured at  $I_C=4.0\text{mA}$ ,  $V_{CE}=2\text{V}$ )

## V. CONCLUSION

The COM2 SiGe BiCMOS technology demonstrates speed in excess of 100 GHz yielding sufficient performance for building circuits in the 40 Gb/s product space. Our uniformity data shows that this process is suitable for high volume and low cost manufacturing. Having both  $F_{MAX}$  and  $F_T$  greater than 100 GHz, as a result of the super self-aligned device structure, makes this process ideal for a wide range of high performance applications at low power.

## ACKNOWLEDGEMENTS

The authors would like to acknowledge Jan W. De Blauwe, for coordinating the project, as well as Mark Decker, Brenda Prenitzer and L. Bizzarro for their help and dedication.

## REFERENCES

- [1] M. Carroll et. al., "COM2 SiGe Modular BiCMOS Technology for Digital, Mixed-Signal, and RF Applications", IEDM Tech. Dig., pp. 145-148, 2000.

- [2] C. King, et. al., "Very Low Cost Graded SiGe Base Bipolar Transistors for a High Performance Modular BiCMOS Process," IEDM Tech. Dig., pp. 565-568, 1999.

- [3] R. McPartland, et. al, Symp on VLSI Circuits, 2000

- [4] M. Frei, et. al., "Integration of high-Q Inductor in a Latch-up Resistant CMOS Technology," IEDM Tech. Dig., pp. 757-760, 1999.